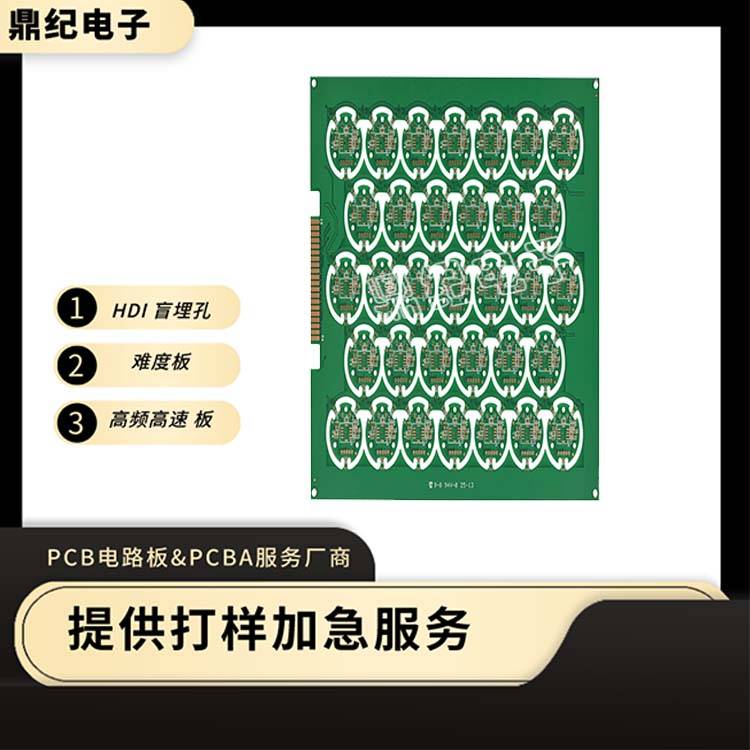

鼎纪电子-优化6层PCB设计,确保高频性能与电气稳定性

2025-04-20

在高速数字与射频电路设计中,6层PCB因其优异的层叠灵活性和成本效益,成为复杂电路的首选。然而,高频信号传输带来的信号完整性(SI)、电源完整性(PI)及电磁兼容性(EMC)问题,直接决定了设备的可靠性与性能。如何通过优化设计规避风险?我们的专业解决方案助您突破技术瓶颈!

️1. 层叠结构优化:平衡信号与电源完整性

合理的层叠设计是高频PCB的核心。我们采用**“信号-地-电源-信号”对称结构**,确保高速信号层紧邻完整参考平面,减少串扰与回流路径阻抗。例如:

- ️Top层:高速信号走线(如差分对)

- ️内层2:完整地平面(降低EMI)

- ️内层3:电源平面(低阻抗供电)

- ️Bottom层:低频信号与关键控制线

通过仿真验证阻抗匹配(如50Ω单端/100Ω差分),避免信号反射导致的波形畸变。

️2. 高频材料选择:降低损耗与介电常数波动

普通FR4材料在高频下损耗(Df)显著增加。我们推荐:

- ️Rogers RO4350B(εr=3.48, Df=0.0037)用于射频关键区域

- ️Isola I-Tera MT40(低损耗,适用于10GHz+设计)

- 结合混合叠层技术,在成本与性能间取得最优解。

️3. 电源完整性(PI)与去耦网络设计

高频电路对电源噪声极为敏感。我们通过:

展开全文- ️分立式去耦电容布局:在电源平面入口、IC供电引脚就近放置0402/0201电容,覆盖宽频段(如1nF+10μF组合)。

- ️平面分割优化:避免电源层跨分割导致回流路径断裂,采用“星型拓扑”降低ΔI噪声。

️4. 严格EMC设计规范

- ️3W规则:关键信号线间距≥3倍线宽,抑制串扰。

- ️接地过孔阵列:在信号换层处密集布置地过孔,提供低阻抗回流路径。

- ️屏蔽腔与包地处理:对敏感信号(如时钟线)实施“地线包围”,减少辐射。

️5. 仿真驱动设计(DFx)

依托️ANSYS HFSS和️Cadence Sigrity工具,我们在设计阶段完成:

- 时域反射(TDR)分析

- 电源网络阻抗扫描(目标<1Ω@100MHz)

- 近/远场EMI预测

️结语

6层PCB的高频性能优化是系统工程。从材料选型到仿真验证,我们提供️全流程技术托管服务,助您的产品在5G、雷达、高速计算等领域实现稳定输出与量产一致性。

️立即联系我们,获取定制化设计方案!